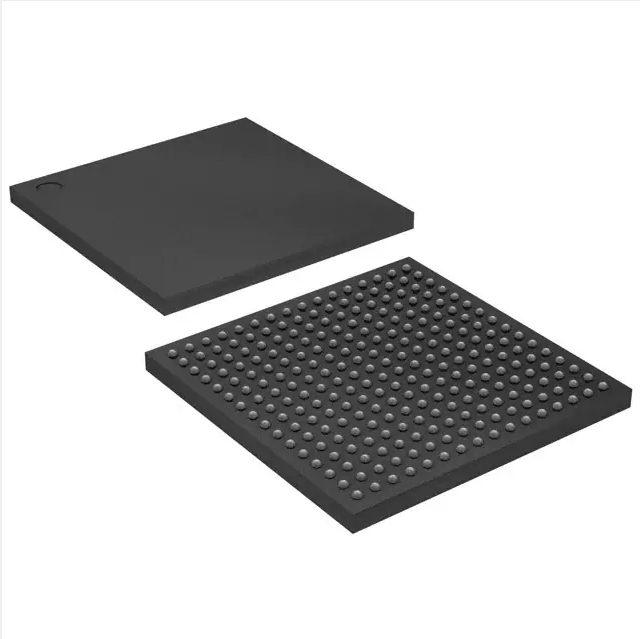

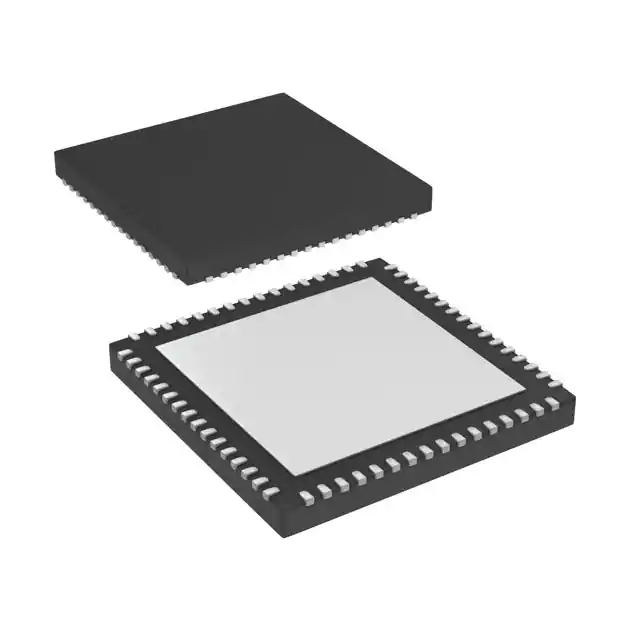

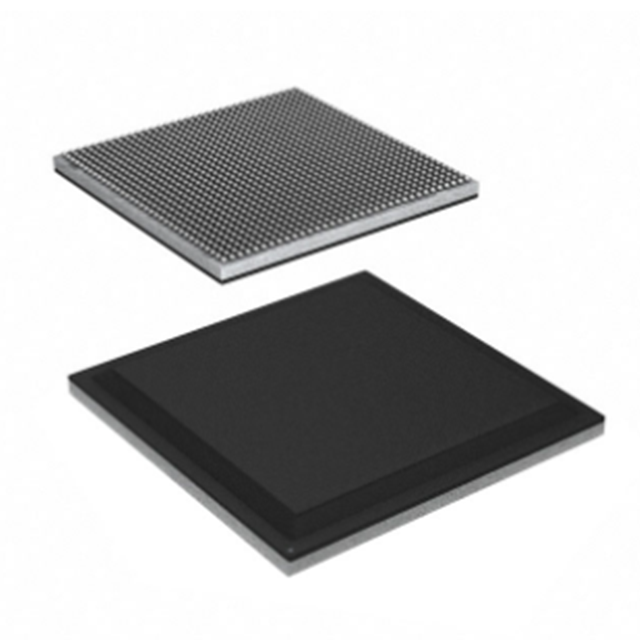

XCZU19EG-2FFVC1760E 100% נייַ & אָריגינעל דק צו דק קאָנווערטער & סוויטשינג רעגולאַטאָר טשיפּ

פּראָדוקט אַטריביוץ

| פּראָדוקט אַטריביוט | אַטריביוט ווערט |

| פאַבריקאַנט: | Xilinx |

| פּראָדוקט קאַטעגאָריע: | SoC FPGA |

| שיפּינג ריסטריקשאַנז: | דער פּראָדוקט קען דאַרפן נאָך דאַקיומענטיישאַן צו אַרויספירן פֿון די פאַרייניקטע שטאַטן. |

| RoHS: | דעטאַילס |

| מאַונטינג נוסח: | SMD/SMT |

| פּעקל / קאַסטן: | פבגאַ-1760 |

| קערן: | ARM Cortex A53, ARM Cortex R5, ARM Mali-400 MP2 |

| נומער פון קאָרעס: | 7 קאָר |

| מאַקסימום זייגער אָפטקייַט: | 600 מהז, 667 מהז, 1.5 גהז |

| L1 קאַש ינסטרוקטיאָן זכּרון: | 2 רענטגענ 32 קב, 4 רענטגענ 32 קב |

| L1 קאַש דאַטאַ זכּרון: | 2 רענטגענ 32 קב, 4 רענטגענ 32 קב |

| פּראָגראַם זכּרון גרייס: | - |

| דאַטן באַראַן גרייס: | - |

| נומער פון לאָגיק עלעמענטן: | 1143450 לע |

| אַדאַפּטיוו לאָגיק מאָדולעס - ALMs: | 65340 אַלם |

| עמבעדיד זכּרון: | 34.6 מביט |

| אַפּערייטינג וואָולטידזש: | 850 מוו |

| מינימום אַפּערייטינג טעמפּעראַטור: | 0 סי |

| מאַקסימום אַפּערייטינג טעמפּעראַטור: | + 100 סי |

| סאָרט: | Xilinx |

| פונאנדערגעטיילט באַראַן: | 9.8 מביט |

| עמבעדיד בלאָק באַראַן - EBR: | 34.6 מביט |

| מויסטשער סענסיטיוו: | יא |

| נומער פון לאָגיק מענגע בלאַקס - לאַבס: | 65340 לאַב |

| נומער פון טראַנססעיווערס: | 72 טראַנססעיווער |

| פּראָדוקט טיפּ: | SoC FPGA |

| סעריע: | XCZU19EG |

| פאַבריק פּאַק קוואַנטיטי: | 1 |

| אונטערקאטעגאריע: | SOC - סיסטעמען אויף אַ טשיפּ |

| האַנדל נאָמען: | Zynq UltraScale + |

ינטעגראַטעד קרייַז טיפּ

קאַמפּערד מיט עלעקטראָנס, פאָטאָנס האָבן קיין סטאַטיק מאַסע, שוואַך ינטעראַקשאַן, שטאַרק אַנטי-ינטערפיראַנס פיייקייט און זענען מער פּאַסיק פֿאַר אינפֿאָרמאַציע טראַנסמיסיע.אָפּטיש ינטערקאַנעקשאַן איז געריכט צו ווערן די האַרץ טעכנאָלאָגיע צו ברעכן דורך די מאַכט קאַנסאַמשאַן וואַנט, סטאָרידזש וואַנט און קאָמוניקאַציע וואַנט.יללומינאַנט, קאַפּאַלער, מאָדולאַטאָר, וואַוועגייד דעוויסעס זענען ינאַגרייטיד אין די הויך געדיכטקייַט אָפּטיש פֿעיִקייטן אַזאַ ווי פאָטאָעלעקטריק ינאַגרייטיד מיקראָ סיסטעם, קענען פאַרשטיין קוואַליטעט, באַנד, מאַכט קאַנסאַמשאַן פון הויך געדיכטקייַט פאָטאָעלעקטריק ינאַגריישאַן, פאָטאָעלעקטריק ינאַגריישאַן פּלאַטפאָרמע אַרייַנגערעכנט III - V קאַמפּאַונד סעמיקאַנדאַקטער מאַנאַליטיק ינאַגרייטיד (INP) ) פּאַסיוו ינטאַגריישאַן פּלאַטפאָרמע, סילאַקאַט אָדער גלאז (פּלאַנאַר אָפּטיש וואַוועגייד, פּלק) פּלאַטפאָרמע און סיליציום-באזירט פּלאַטפאָרמע.

ינפּ פּלאַטפאָרמע איז דער הויפּט געניצט פֿאַר די פּראָדוקציע פון לאַזער, מאָדולאַטאָר, דעטעקטאָר און אנדערע אַקטיוו דעוויסעס, נידעריק טעכנאָלאָגיע מדרגה, הויך סאַבסטרייט פּרייַז;ניצן פּלק פּלאַטפאָרמע צו פּראָדוצירן פּאַסיוו קאַמפּאָונאַנץ, נידעריק אָנווער, גרויס באַנד;די ביגאַסט פּראָבלעם מיט ביידע פּלאַטפאָרמס איז אַז די מאַטעריאַלס זענען נישט קאַמפּאַטאַבאַל מיט סיליציום-באזירט עלעקטראָניק.די מערסט באַוווסט מייַלע פון סיליציום-באזירט פאָטאָניק ינטאַגריישאַן איז אַז דער פּראָצעס איז קאַמפּאַטאַבאַל מיט CMOS פּראָצעס און די פּראָדוקציע קאָס איז נידעריק, אַזוי עס איז גערעכנט ווי די מערסט פּאָטענציעל אָפּטאָעלעקטראָניק און אפילו אָפּטיש ינטאַגריישאַן סכעמע.

עס זענען צוויי ינאַגריישאַן מעטהאָדס פֿאַר סיליציום-באזירט פאָטאָניק דעוויסעס און CMOS סערקאַץ.

די מייַלע פון די ערשטע איז אַז די פאָטאָניק דעוויסעס און עלעקטראָניש דעוויסעס קענען זיין אָפּטימיזעד סעפּעראַטלי, אָבער די סאַבסאַקוואַנט פּאַקקאַגינג איז שווער און געשעפט אַפּלאַקיישאַנז זענען לימיטעד.די יענער איז שווער צו פּלאַן און פּראָצעס ינטאַגריישאַן פון די צוויי דעוויסעס.דערווייַל, כייבריד פֿאַרזאַמלונג באזירט אויף יאָדער פּאַרטאַקאַל ינטאַגריישאַן איז דער בעסטער ברירה